Commodore 16: CPU 7501/8501 FPGA Replacement

Uno dei maggiori problemi che affliggono gli utenti dei retro-computer Commodore della serie 264 (C16, Plus/4, C116) è rappresentato dalla fragilità della CPU, il processore MOS 7501/8501. Scalda molto e molto velocemente, ed è uno dei due componenti che si rompono più facilmente, specie dopo un bel trentennio di vita.

Implementazione FPGA

Fortunatamente la tecnologia FPGA ci viene in aiuto, permettendo di re-implementare teoricamente qualunque chip del passato… pur di trovare qualcuno in grado di farlo! 🙂

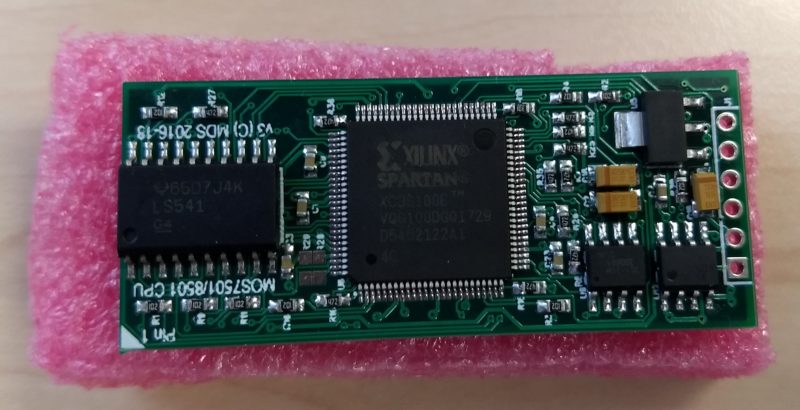

Piotr Bugaj e Mark Smith hanno realizzato un componente sostitutivo della CPU 7501/8501 completamente in FPGA, al momento venduto sul sito SellMyRetro al prezzo di 40 sterline inglesi. Eccolo nella sua interezza:

Notare in basso a sinistra la freccetta bianca con l’indicazione “1”: indica il verso corretto di inserimento nello zoccolo, basta far corrispondere il simbolo “1” della FPGA con il simbolo “1” presente sulla scheda del C16.

Si tratta di una FPGA Xilinx già programmata e pronta all’uso: basta semplicemente sostituirla alla CPU guasta e richiudere il tutto. Si incastra perfettamente nel case senza alcuna sbavatura, eccola qui, tra il modulatore TV (sopra) e il TED (sotto):

Accensione e test

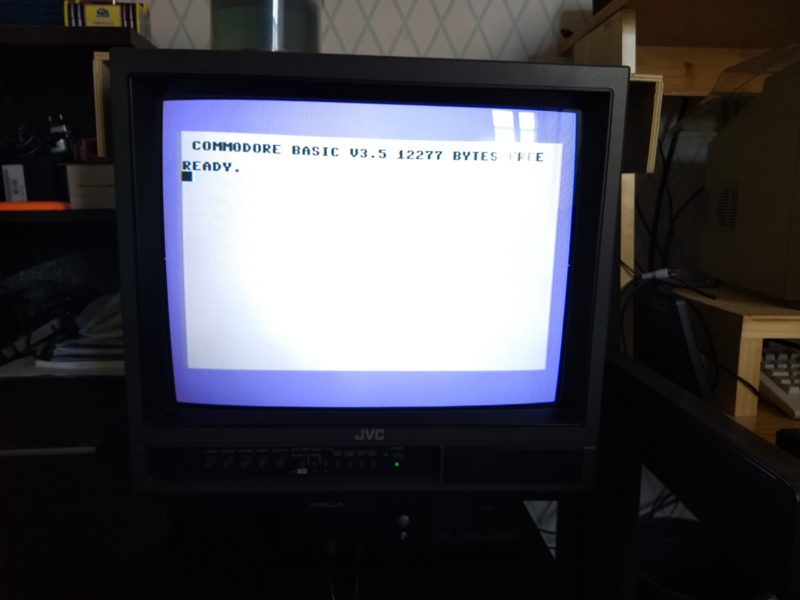

Una volta richiuso il case, possiamo accendere il tutto e con un po’ di suspance… ecco il risultato:

Un C16 redivivo e funzionante. Non è necessario un dissipatore perché a differenza del 7501 originale, questa FPGA scalda pochissimo.

Come primo test ho provato a caricare una delle cassette del corso VideoBASIC del Gruppo Editoriale Jackson:

Il caricamento della cassetta di VideoBASIC non è casuale, perché questo nastro ha due caratteristiche peculiari:

- L’uso di un fastloader che utilizza le halfwaves, tipiche della serie 264

- Comprende più programmi in sequenza, lasciando in pausa il caricamento tra l’esecuzione di un programma e il caricamento del successivo

In particolare il secondo punto: la CPU 7501/8501 ha un pin dedicato al “Motor ON/OFF” del datassette. In pratica questo pin manda al datassette il segnale di “pausa” alla fine di un caricamento: il motore si ferma pur essendo ancora premuto il tasto PLAY. Ciò è essenziale quando su una cassetta ci sono più “capitoli” da leggere.

Il test ha avuto esito positivo, il corso è stato caricato con successo in ogni suo capitolo.

Test con illegal opcodes: il caso LAX (update 16/05/2018)

Leggendo vari post che parlano della soluzione FPGA, si è parlato dei cosiddetti illegal opcodes: si tratta di istruzioni macchina non esplicitamente previste dai progettisti, ma che sono state implementate come “effetto collaterale”, diciamo “per caso”.

Questi illegal opcodes (detti anche unintended opcodes) sono importanti perché alcuni di essi sono risultati essere alternative molto più efficienti in termini di tempo rispetto all’equivalente sequenza “canonica” di istruzioni.

Per tale motivo questi opcodes sono stati a volte usati dai programmatori per ottimizzare il loro lavoro, è pertanto un test importante capire se questa implementazione FPGA della CPU 7501/8501 implementi o no questi casi.

LAX: LDA + TAX

Una delle istruzioni macchina “illegali” più utilizzate è la cosiddetta LAX: rappresenta la combinazione di LDA + TAX, ma eseguita nella metà del tempo. Per i meno avvezzi, LDA è l’istruzione che scrive un valore nel registro A (accumulatore), mentre TAX copia il contenuto del registro A nel registro X. Utilizzeremo l’opcode con indirizzamento assoluto: il valore da scrivere nel registro A verrà cioè letto da un indirizzo di memoria.

L’opcode di LAX con indirizzamento assoluto è $AF. Per effettuare questo test leggeremo il valore da scrivere in A (e contemporaneamente in X) dalla prima cella (in alto a sinistra) dello schermo, cioè la locazione $0C00 (dec 3072), quindi scriveremo il valore di A nel registro TED che controlla il colore dello sfondo ($FF15), e il valore di X nel registro del colore del bordo ($FF19).

Se il test avrà esito positivo, lo sfondo e il bordo dovranno avere lo stesso colore.

Come sarebbe in assembly (org=$2000, dec 8192)

.C:2000 AF 00 0C LAX $0C00 .C:2003 8D 15 FF STA $FF15 .C:2006 8E 19 FF STX $FF19 .C:2009 60 RTS

…peccato però che non sia possibile inserirlo in questo modo con il monitor assembly integrato nel C16, dato che l’istruzione LAX, per l’appunto, è unintended e pertanto non prevista dai progettisti. Lo scriveremo quindi…

In esadecimale (org=$2000, dec 8192)

>2000 AF 00 0C 8D 15 FF 8E 19 >2008 FF 60

Provando quindi a disassemblare attraverso il monitor integrato sarà confermato il fatto che LAX non era un’istruzione prevista, e pertanto verrà “disassemblata” come “opcode non riconosciuto” attraverso tre punti interrogativi (???):

Nell’ultima riga si nota la preparazione per l’esecuzione: scriviamo il valore 53 nella locazione 3072 e lanciamo (ovviamente su un Commodore 16 dotato della CPU in FPGA in esame!) la nostra routine di test (SYS 8192). Ecco il risultato:

Sfondo e bordo hanno lo stesso colore, che è stato prelevato separatamente dal registro A e dal registro X: pertanto il test ha avuto esito positivo, l’istruzione illegale LAX funziona.

È possibile verificare in modo simile anche gli altri illegal opcodes.

Alternative alla soluzione FPGA

Esiste una soluzione alternativa all’uso di questa FPGA, che è un adattatore che consente di montare sullo zoccolo del 7501 un più comune MOS 6510 prelevato da un Commodore 64. Questa soluzione ha il vantaggio di essere più economica, ma presenta tre svantaggi:

- La CPU 6510 è comunque un componente vecchio che si porta dietro i suoi anni e i suoi problemi di “surriscaldamento”

- Non è possibile inviare il segnale di “Motor ON/OFF” al datassette per cui il motore continuerà a girare anche dopo la fine di un caricamento, rendendo problematico l’utilizzo di nastri (o file TAP se si usano Tapuino o una Princess V3) con più “capitoli” all’interno

- Necessita di un KERNAL modificato, per cui eventuali programmi che utilizzano specifiche chiamate a sistema potrebbero non funzionare

Conclusioni

La replica FPGA di Piotr Bugaj & Mark Smith sembra essere un ottimo prodotto, a un prezzo decisamente onesto sia per quanto riguarda la qualità che per il fatto stesso di permettere di recuperare al 100% le funzionalità di un C16 o un Plus/4 altrimenti “defunti”.

Ringraziamenti

Ringrazio Filippo Maggioni per le preziose informazioni, per le prove effettuate e per la sua realizzazione di Tapuino che è stata utilizzata nelle prove.

Link esterni

- Sell My Retro: MOS 7501/8501 CPU replacement for C16/116/+4 by Piotr Bugaj & Mark Smith

- Cassette di VideoBASIC per C16, dumpate da Massi cadenti, su EdicolaC64

- Elenco degli opcode dei processori della famiglia 6502, compresi gli illegal/unintented